[ad_1]

A team of hardware architects working with Pixilica is developing an open-source graphics unit for systems-on-chip with the RISC-V processor instruction set – called RV64X. The vector instruction set already specified by RISC-V, around which a complete GPU is designed, serves as the development basis.

A small RISC-V CPU core with a docked RV64X GPU is plannedthat can be accommodated in a chip design as often as required. If desired, developers can add a stronger, custom RISC-V CPU as the main processor or use the standard design alone. In addition, Pixilica wants to disclose a showcase implementation that can be adapted to special needs.

Cheap standard GPU

RV64X is intended for programmable logic chips (FPGAs) and application-specific integrated circuits (ASICs) in order to take over 3D or compute calculations and to output a display image. So far, RISC-V processors have relied on purchased – and proprietary – third-party GPUs for image output if the resources are not invested in in-house development. The single-board computer BeagleV, for example, will in future come with a graphics chip from Imagination Technologies.

Low-end GPUs with the RV64X instruction set are planned for the start, but more powerful versions could come later. Like the news portal, it should take at least two years for an initial implementation EE Times notes.

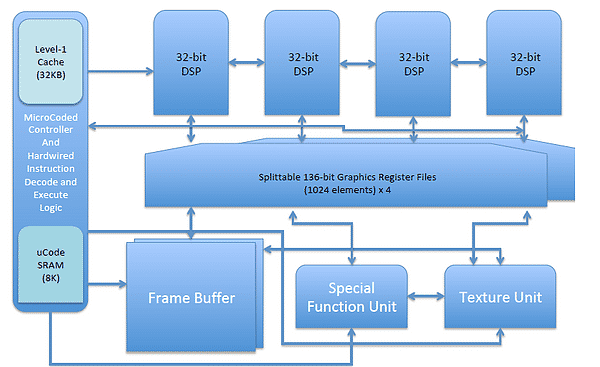

(Image: Pixilica)

Pixilica provides shader cores that can handle fixed and floating point numbers up to 32 bits deep (FP32). 8-bit integer operations (INT8) are also suitable, for example, for executing neural networks (inference). Programming should initially be possible via the Vulkan graphics API; OpenGL and DirectX follow.

(mma)

[ad_2]